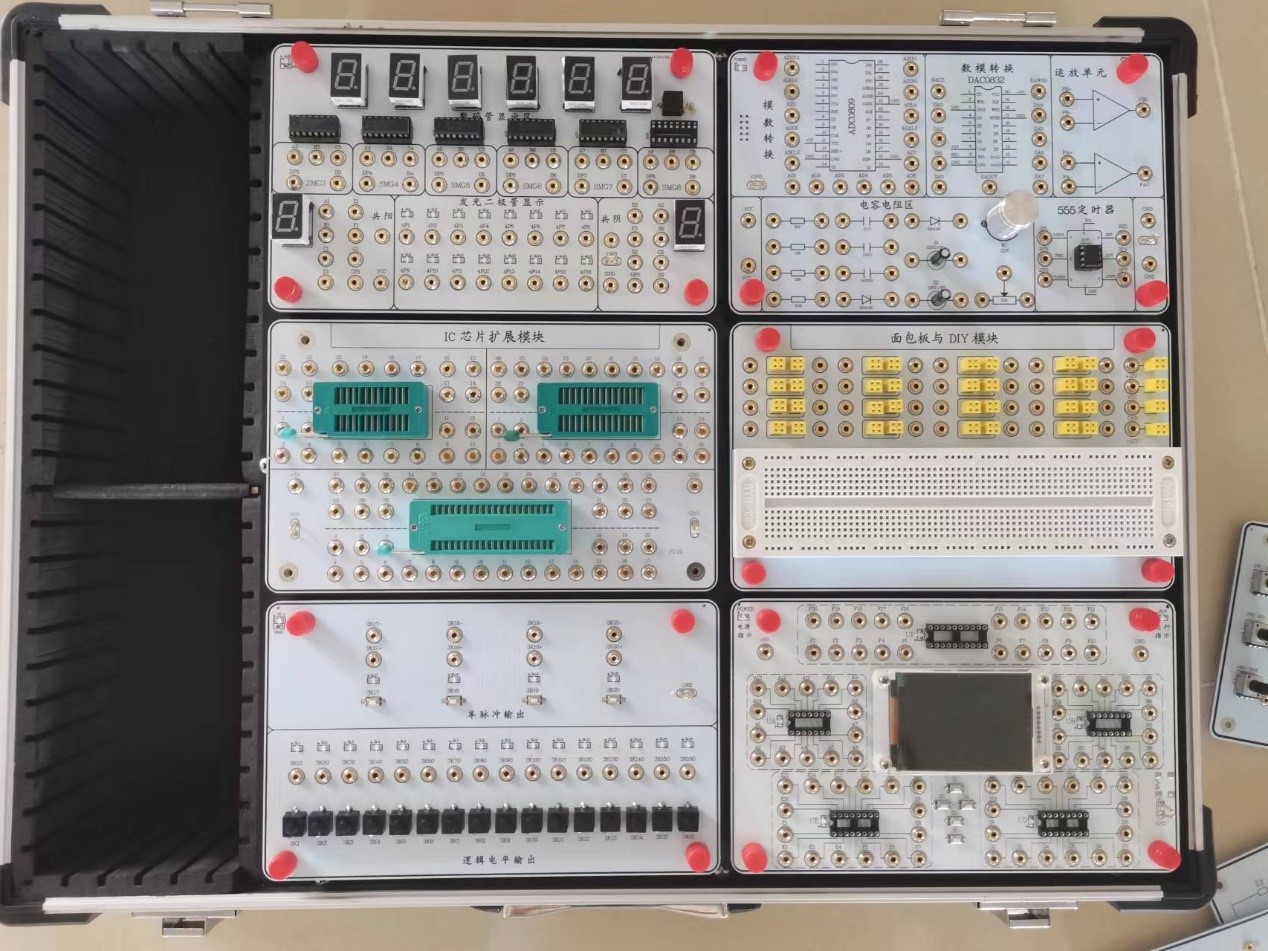

實驗箱采用模塊結(jié)構(gòu)設(shè)計,實驗箱接插件可靠,連線及測試錨孔采用內(nèi)徑為Φ2自鎖緊式插孔,使用直觀、可靠、維修方便、簡捷。學(xué)生可按照各實驗項目自已動手搭建電路,培養(yǎng)學(xué)生的思維能力及動手能力。

技術(shù)指標(biāo):

1.實驗箱由以下實驗?zāi)K單元組成:ADDA實驗?zāi)K、邏輯電平實驗?zāi)K、時鐘信號產(chǎn)生模塊、數(shù)碼管顯示模塊、DIP插座開發(fā)模塊、開發(fā)設(shè)計模塊組成。

2.時鐘信號產(chǎn)生模塊:提供1Hz、10Hz、500Hz、1kHz、2kHz、5kHz、10kHz、20kHz、100kHz、500kHz;邏輯筆可用于測試高電平、低電平及高阻態(tài);兩路可調(diào)直流電壓輸出:0~5V;蜂鳴器等。

3.邏輯電平實驗?zāi)K:提供16路邏輯電平開關(guān)、4個單脈沖輸出開關(guān)輸出端自帶顯示電路,直觀顯示開關(guān)量的輸出狀態(tài),同時輸出端帶保護功能。

4.數(shù)碼管顯示模塊:提供6位LED數(shù)碼顯示器,自帶BCD碼譯碼電路;4位獨立數(shù)碼管,可裝共陽或共陰數(shù)碼管,都設(shè)計有限流電阻以保護數(shù)碼管。

5.ADDA實驗?zāi)K:提供基于FPGA實現(xiàn)的模數(shù)轉(zhuǎn)換(ADC0809)、數(shù)模轉(zhuǎn)換(DAC0832)功能,可完成AD、DA相關(guān)實驗內(nèi)容、提供555定時器單元及實驗所需的電阻、電容、運放等實驗器件。

6.DIP插座開發(fā)模塊:含IC14、IC16插座各兩個,雙列圓孔插座,穩(wěn)定耐用,方便芯片插拔。

7.配置FPGA開發(fā)模塊,要求FPGA芯片不低于 AITERA EP4CE6E22C8N 要求FPGA IO口獨立引出,方便學(xué)生設(shè)計開發(fā),提供轉(zhuǎn)換接口,方便與實驗箱連接。要求FPGA開發(fā)模塊能夠與DIP插座模塊聯(lián)動,可以完成芯片映射功能,即DIP插座可以插74系列芯片做實驗,也可通過人機交互接口(USB口)在DIP插座上映射74系列芯片(不插芯片)做實驗。

8.開發(fā)設(shè)計模塊:提供自主設(shè)計開發(fā)區(qū)域,區(qū)域19 CM *18CM,配套出口品質(zhì)面包板,磷青銅彈片;提供18個實驗轉(zhuǎn)換接插端子,方便學(xué)生與實驗箱連接實驗。

9.內(nèi)置+5V、+12V、-12V電源,電源具有短路保護及自動恢復(fù)功能。

10.實驗項目:

基本實驗: 實驗箱的使用、門電路邏輯功能及測試 、三態(tài)門和OC門的研究、組合邏輯電路(半加器、全加器) 、編碼器與譯碼器、數(shù)據(jù)選擇器、觸發(fā)器及其功能轉(zhuǎn)換、移位寄存器、組合電路中的競爭與冒險等。

應(yīng)用設(shè)計實驗 :邏輯門的應(yīng)用、計數(shù)譯碼與顯示、 MSI計數(shù)器的應(yīng)用、雙向移位寄存器應(yīng)用、累加器的設(shè)計、格雷碼與自然二進制碼轉(zhuǎn)換器、十翻二運算電路設(shè)計等。

配套FPGA開發(fā)實驗:隨機存儲器及其應(yīng)用、動態(tài)掃描顯示電路設(shè)計、電機驅(qū)動、PID算法、邏輯電路、時序電路設(shè)計、紅綠燈、流水燈、流量計數(shù)、信號檢測與處理、對數(shù)乘法器的設(shè)計實驗、基于FPGA的樓道聲控延時燈設(shè)計、電子鐘設(shè)計性項目。

EDA實驗內(nèi)容:基于Quartus II基本庫元件的原理圖設(shè)計、基于Quartus II宏功能模塊的原理圖設(shè)計、基于原理圖的計數(shù)器設(shè)計;用VHDL設(shè)計實現(xiàn)模8計數(shù)器、用VHDL設(shè)計實現(xiàn)常用組合邏輯電路、用VHDL設(shè)計常用時序電路。